# USING INFORMATION FLOW TO DESIGN AN ISA THAT CONTROLS TIMING CHANNELS

DREW ZAGIEBOYLO G. EDWARD SUH ANDREW C. MYERS

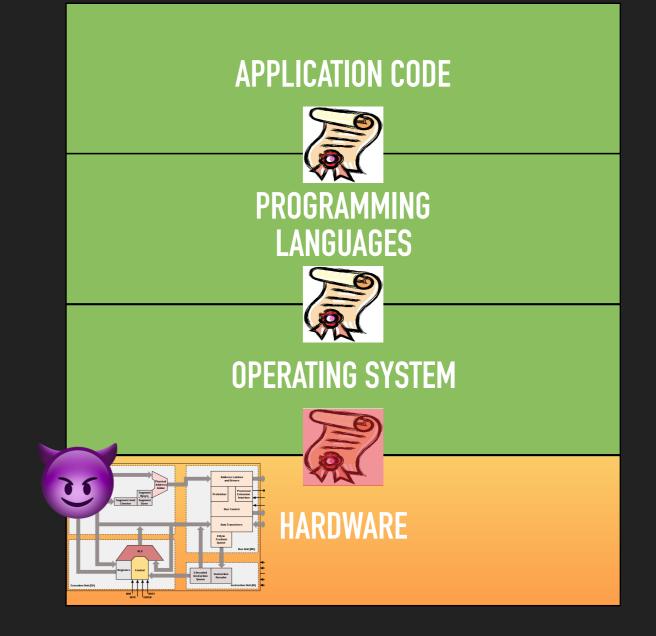

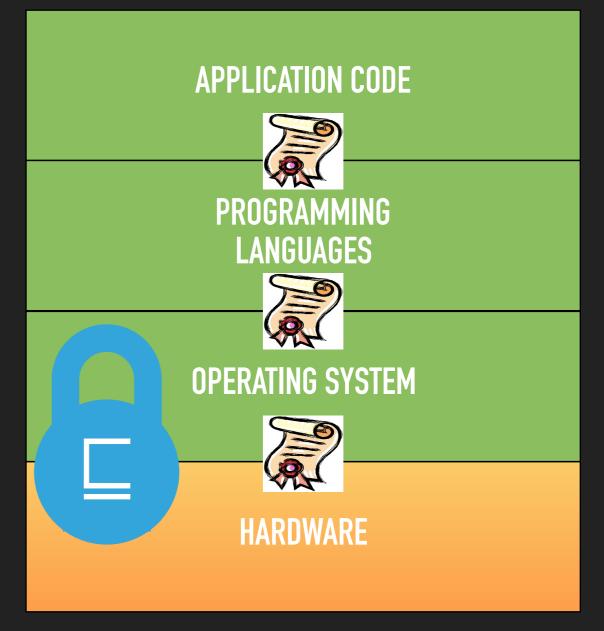

WE NEED A NEW HW-SW CONTRACT (ISA) TO CONTROL MICROARCHITECTURAL TIMING CHANNELS

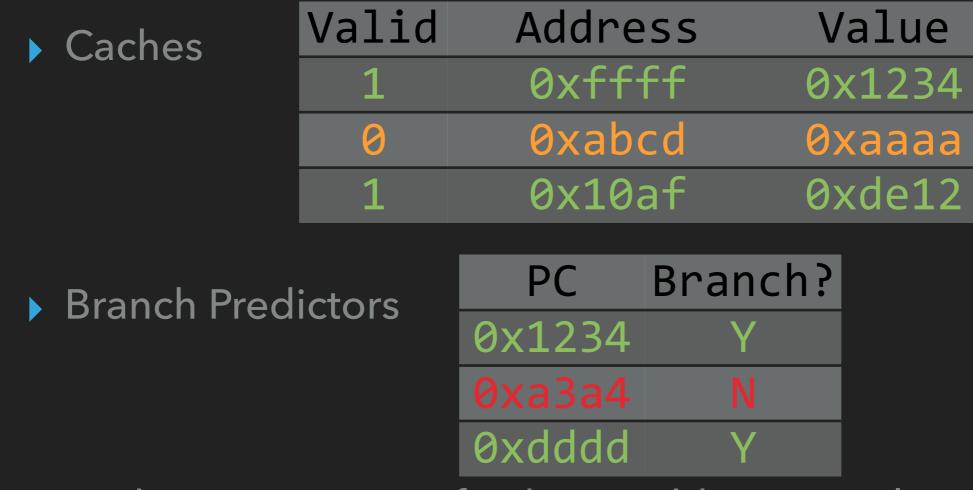

### MICROARCHITECTURE

- Unspecified CPU behavior + state

- Primarily affect performance

Arithmetic Units, Prefetchers, Address Translators,

Fill buffers, Memory Arbiters, Pipeline State, etc.

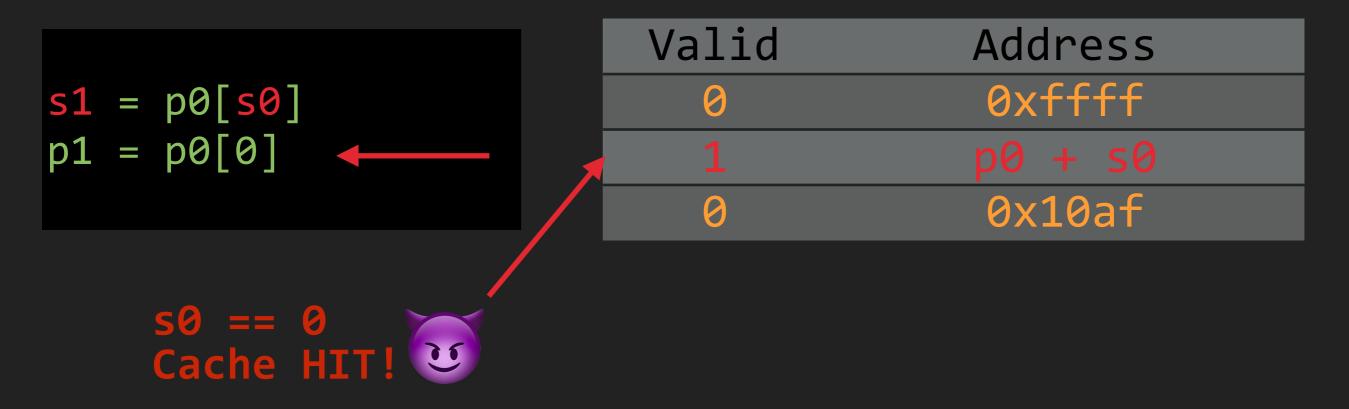

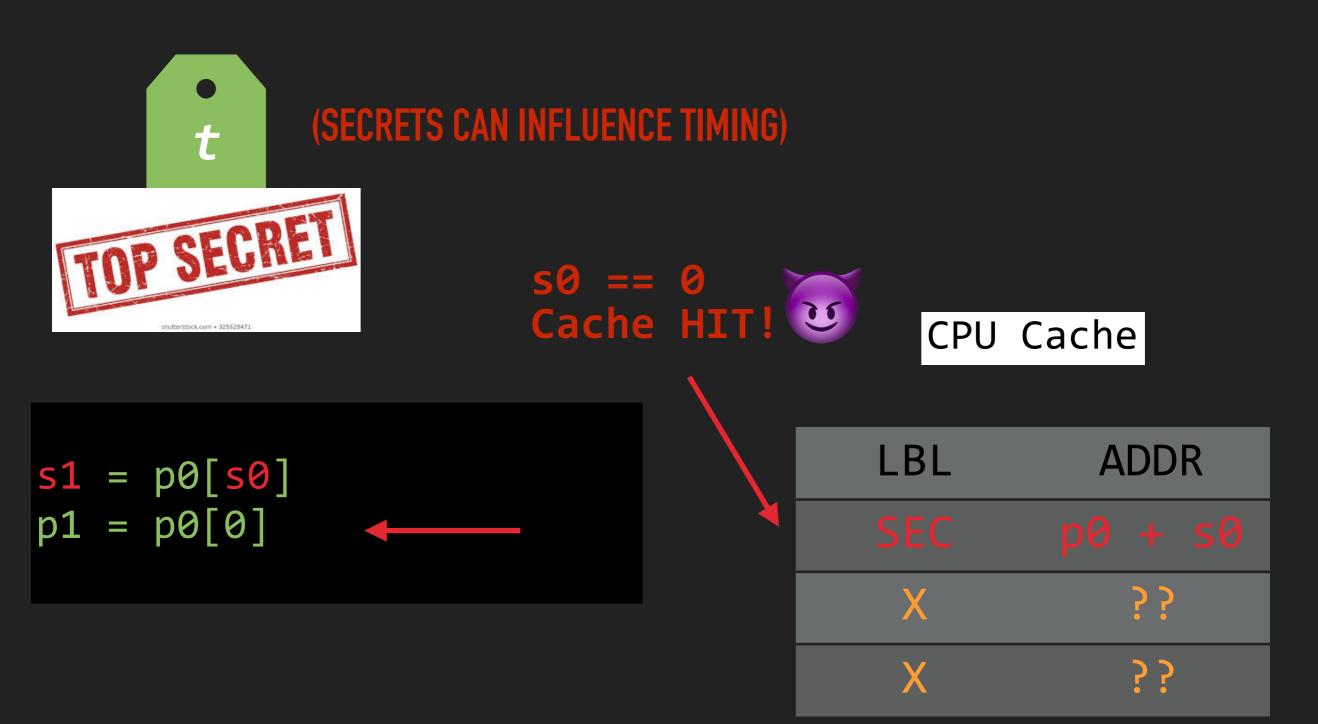

Essence of the *Meltdown ('18)* attack

#### CPU Cache

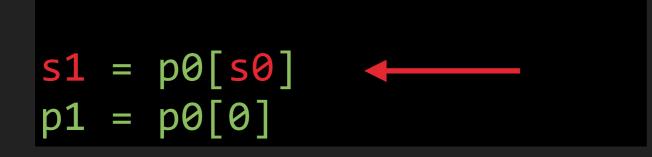

s1 = p0[s0]

p1 = p0[0]

| Valid | Address |  |

|-------|---------|--|

| 0     | 0xffff  |  |

| 0     | 0xabcd  |  |

| 0     | 0x10af  |  |

Essence of the *Meltdown ('18)* attack

| Valid | Address |  |

|-------|---------|--|

| 0     | 0xffff  |  |

| 0     | 0xabcd  |  |

| 0     | 0x10af  |  |

Essence of the *Meltdown ('18)* attack

| Valid | Address |  |

|-------|---------|--|

| 0     | 0xffff  |  |

| 1     | p0 + s0 |  |

| 0     | 0x10af  |  |

Essence of the *Meltdown ('18)* attack

#### INTRODUCTION

### MICROARCHITECTURAL SIDE CHANNELS

Meltdown ('18)

RIDL ('19) Zombieload ('19)

#### INTRODUCTION

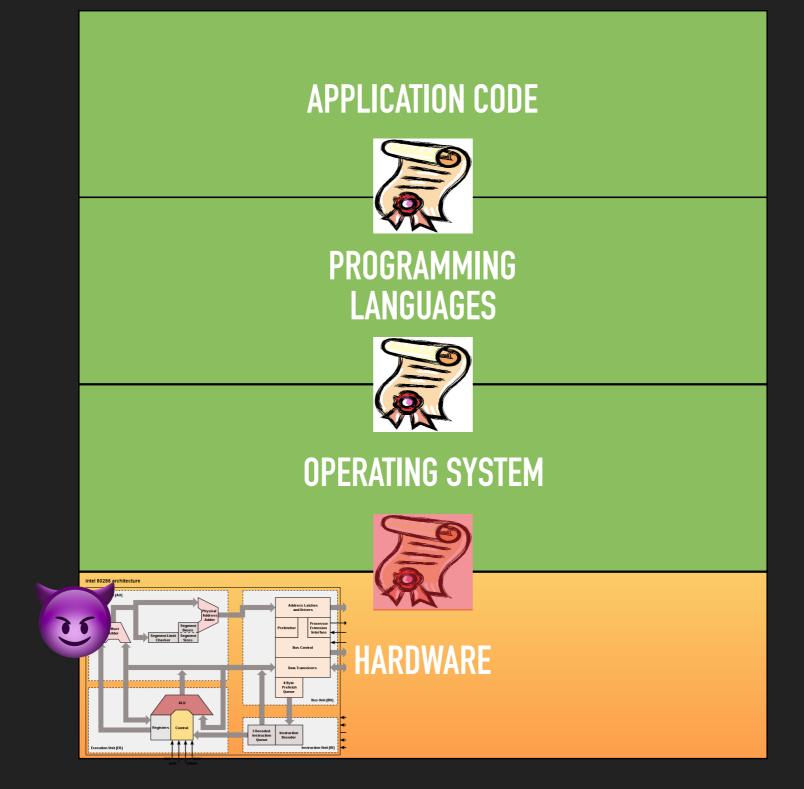

### MITIGATING MICROARCHITECTURAL SIDE CHANNELS

### MITIGATING MICROARCHITECTURAL SIDE CHANNELS

Microarchitectural side channels bypass current contracts

Need a HW-SW co-design mitigation mechanism

## THIS PAPER: INFORMATION FLOW CONTROL ISA

- 1. Sound and portable contract for secure SW design

- Extension of RISC-V

- Timing-Sensitive

Noninterference

- 2. Guide to HW designers

- Microarchitectural Noninterference

- No implementation details

- 3. Practical ISA Features

- Constrained Downgrading

- Control Transfer Primitives

## DYNAMIC IFC CONTRACT

- Software controls IFC labels

- Labels are mutable state

- SW must explicitly change architectural labels

- Hardware enforces policies at runtime

### **FLOATING LABELS**

### **ENFORCING NONINTERFERENCE**

Change existing semantics of RISC-V

add x1, x2, x3

## $L(pc) \sqcup L(x2) \sqcup L(x3) \not\sqsubseteq L(x1)$

$L(pc) \sqcup L(x2) \sqcup L(x3) \sqsubseteq L(x1)$

X1 := X2 + X3

### **ENFORCING NONINTERFERENCE**

Change existing semantics of RISC-V

$$L(x1) \sqcup L(x2) \sqsubseteq L(pc) \quad \text{if } (x1 == s2) \\ \text{then } PC := LOC$$

## $L(x1) \sqcup L(x2) \not\sqsubseteq L(pc)$ NO-OP

## SIMILAR RESTRICTIONS ON OTHER INSTRUCTIONS

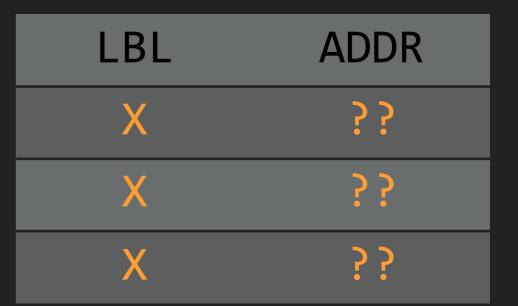

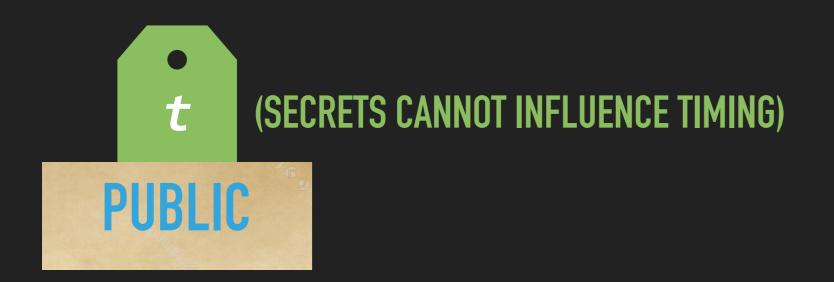

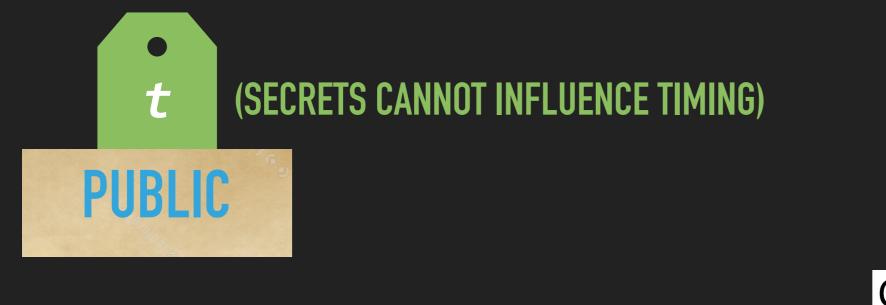

- How does software control timing?

- State that influences timing ⊑ t

Language-based Timing Mitigation [Zhang et al. '12]

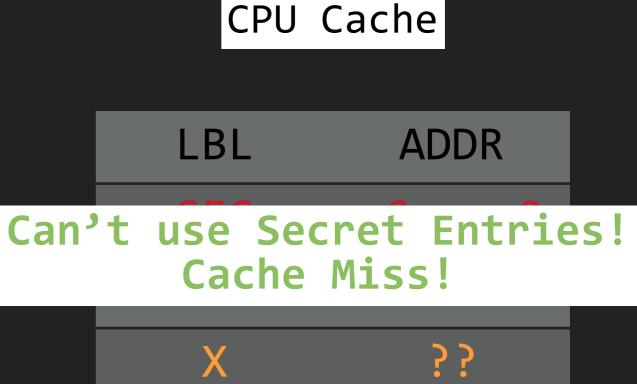

## s1 = p0[s0] p1 = p0[0]

| LBL | ADDR       |

|-----|------------|

| X   | ??         |

| X   | <u>;</u> ; |

| X   | ??         |

s1 = p0[s0]

p1 = p0[0]

p1 = p0[0]

| LBL | ADDR       |  |

|-----|------------|--|

| SEC | p0 + s0    |  |

| X   | <b>?</b> ? |  |

| X   | <b>;</b> ; |  |

| LBL | ADDR       |

|-----|------------|

| X   | <b>?</b> ? |

| X   | <b>;</b> ; |

| X   | ??         |

| LBL | ADDR       |  |

|-----|------------|--|

| SEC | p0 + s0    |  |

| X   | <u>;</u> ; |  |

| X   | <u>;</u> ; |  |

### MICROARCHITECTURAL NONINTERFERENCE

- Software controls data and timing labels

- Hardware ensures timing and microarchitecture observe noninterference

$$\begin{aligned} \forall C_1, C_2 . (C_1 =_L C_2) \land (C_i \rightarrow C_i') \\ \implies (C_1'[\mu] =_L C_2'[\mu]) \land (C_1'[t] =_L C_2'[t]) \end{aligned}$$

$$\begin{aligned} & \text{MICROARCHITECTURAL} \\ & \text{STATE} \end{aligned}$$

$$\begin{aligned} & \text{INSTRUCTION DURATION} \end{aligned}$$

### MICROARCHITECTURAL NONINTERFERENCE

$$\forall C_1, C_2 . (C_1 =_L C_2) \land (C_i \rightarrow C'_i)$$

$$\implies (C'_1[\mu] =_L C'_2[\mu]) \land (C'_1[t] =_L C'_2[t])$$

- Implementation independent

- Allows many performance optimizations (e.g. speculation)

- HW designer must prove implementation safe

### **IFC SECURITY GUARANTEES**

| Security<br>Guarantee  | Requires Static<br>Enforcement | Requires Compiler<br>Changes |

|------------------------|--------------------------------|------------------------------|

| TS-<br>Noninterference | Y                              | Y                            |

| TS-<br>Nonmalleability | Ν                              | Y                            |

| Legacy Isolation       | Ν                              | N                            |

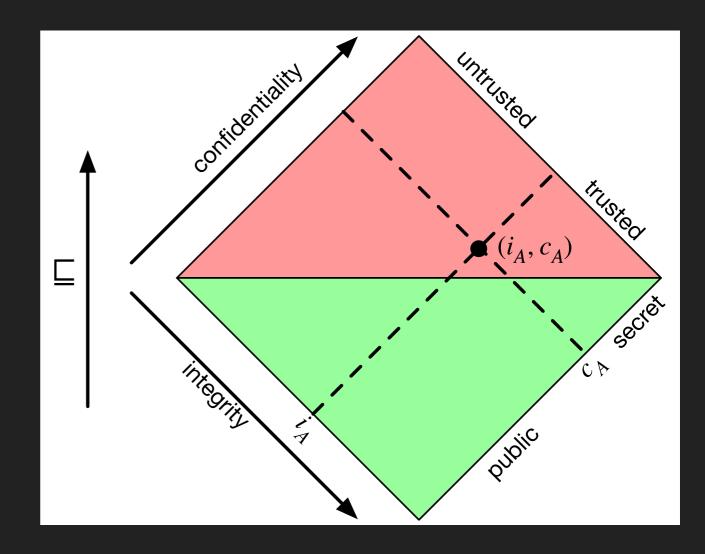

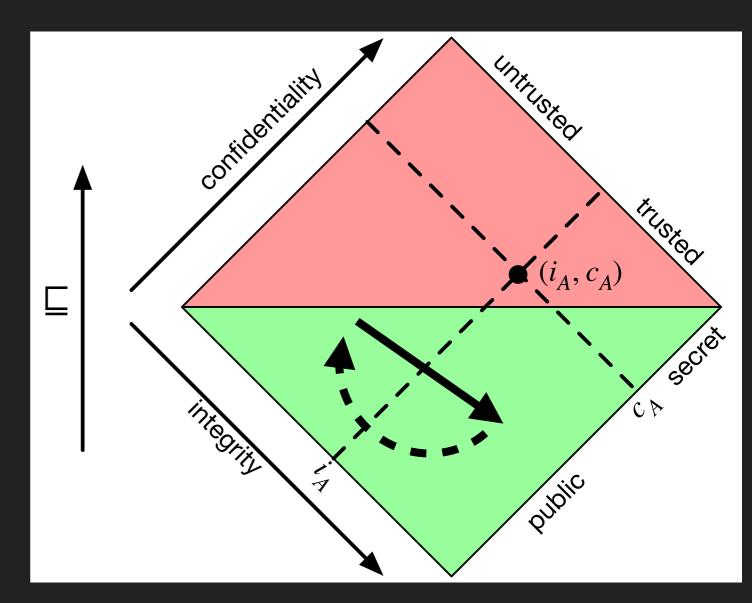

### **CONSTRAINING DOWNGRADING**

Downgrades violate noninterference

- Declassification, Endorsement

- Nonmalleable Information Flow [Cecchetti et al. '17]

- Robust Declassification + Transparent Endorsement

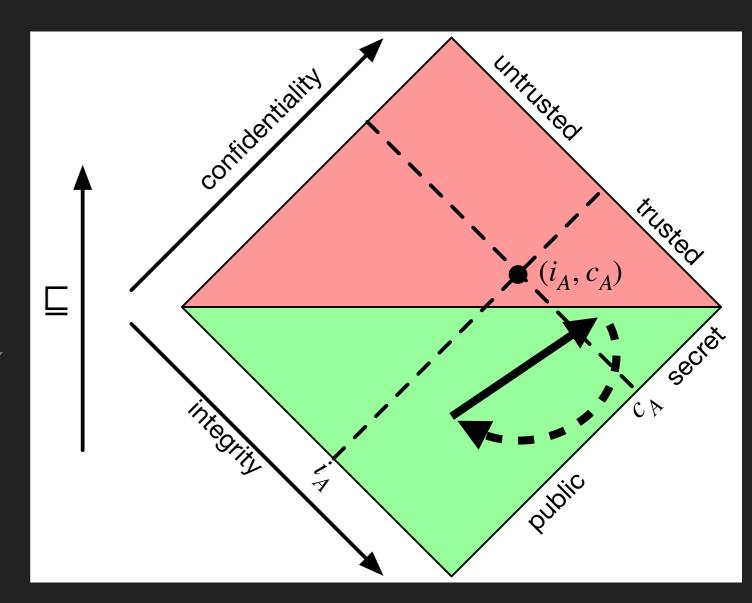

### **CONSTRAINING DOWNGRADING**

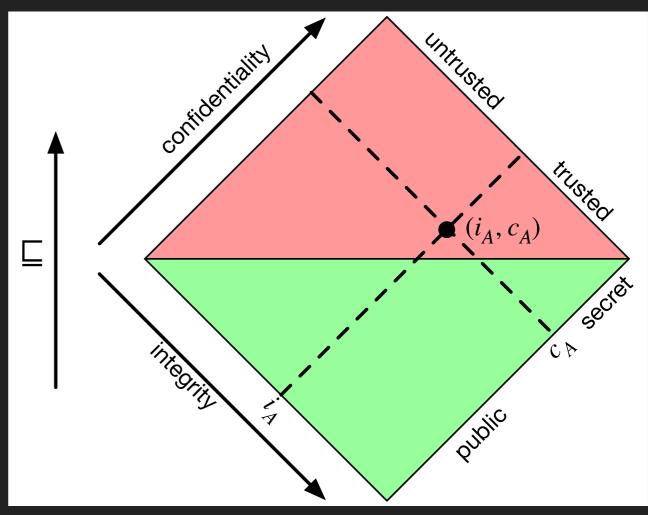

- Key Idea: Compromised data may not be downgraded

- Compromised = More secret than trustworthy

## **CONSTRAINING DOWNGRADING**

- Compromised = More

secret than trustworthy

- Novel contribution:

- More general re-label restrictions in dynamic label setting

- Must keep pc uncompromised

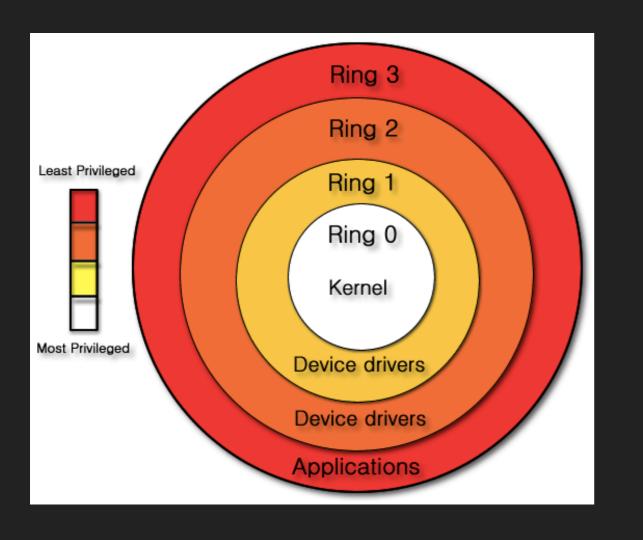

### **CONTROL TRANSFER**

- Required for sharing HW across security domains

- System Calls and other HW primitives provide support

- Protection Rings are an instance of a Lattice

### Call Gates

Generalized control transfer for a lattice policy

### **CALL GATES**

- Upcalls

- Establish return conditions a priori

- Primitive for black-box timing mitigation [Zhang et al. '12]

- Primitive for sandboxing

### **CALL GATES**

- Downcalls

- Analogous to system calls

- Pre-register entry points

## WE PROVIDE OTHER CONSTRAINTS ON CALL GATES TO PROVE NONMALLEABILITY

### MORE TECHNICAL DETAILS IN PAPER / TECHNICAL REPORT

- Attacker model, low equivalence relation, more explicit restrictions and *full proofs* of *Timing-Sensitive Noninterference TS-Nonmalleable Information Flow*

- Discussion on Exception Handling + Asynchrony

- Example Programs + Call Gate Usage

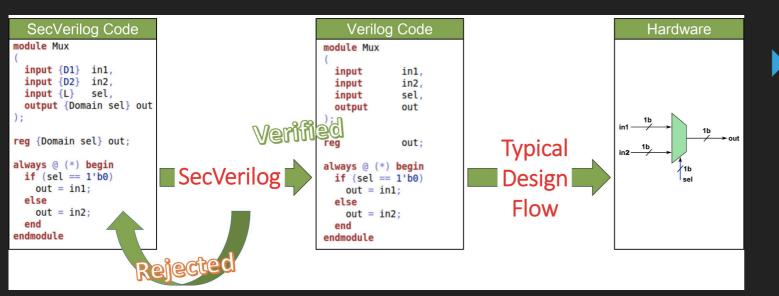

## **FUTURE WORK**

Model multicore and concurrency ISA operations

- How do we verify that HW satisfies Microarchitectural NI?

- Existing tools not expressive enough (SecVerilog '12, '19)

### CONCLUSION

- General and portable contract for secure SW design

- Microarchitecural NI Security Condition Guides Secure HW Development

- Proof of Timing-Sensitive Noninterference and Timing-Sensitive Nonmalleability

- Practical primitives for downgrading and control transfer

- Nonmalleability w/ Dynamic Labels

- Call Gates provide Generalized Control Transfer

# THANK YOU!